Building the Infinite Brain

My research vision is to build systems that can directly interface with the brain, decode its underlying thoughts, memories, and communicate with it using electrical feedback. Such systems would help advance our understanding of the brain, offer new treatments for debilitating diseases like Parkinson’s and epilepsy, augment the healthy brain, and even enable mind-machine teaming. It would one day enable people to process vast information across the entire internet, just with their thoughts, like an infinite brain. More details are in this seminar I gave at the NSF AI Institute for Edge Computing (Athena).

My work has the synergy of building computer architectures and systems for the brain sciences, and using lessons from their deployment and brain-inspiration to build new systems. I developed BCIs that can process 100s of Mbps neural data on device[TopPicks'24, ISCA'23, HotChips'23], classical and quantum platforms to accelerate computational cognitive modeling frameworks [arXiv'23, CGO'22], techniques to orchestrate data and compute for efficiency and security, designed with brain-inspiration [HotOS'23], control theory [TopPicks'22, ISCA'21, MICRO'19, ISCA'18, ISCA'16, PACT'17], and machine learning [PACT'24, arXiv'23]. I've also been working on understanding the ethical, and legal implications of BCIs, and their influence on hardware design [HotEthics'24].

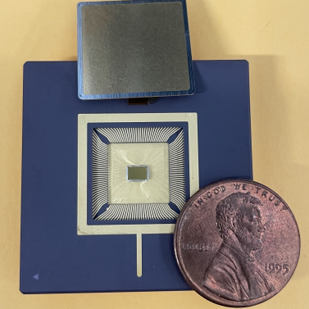

I'm working on taping out my BCI processors in multiple iterations. The initial test chips are back, and I'm closely working with clinicians and neuroscientists at Yale to setup ex vivo tests with them. I'm also working with cognitive neuroscientists at Princeton and Indiana universities to integrate my computational platforms with their modeling.

Prototypes I worked on

HALO/SCALO

HALO/SCALO

Maya (defense for power side channels)

Maya (defense for power side channels)

Tangram server(AMD)

Tangram server(AMD)

Yukta Odroid test board

Yukta Odroid test board

Publications and Patents

Google ScholarPre-prints

-

[arXiv '23] Quantum Cognitive Modeling: New Applications and Systems Research Directions

Raghavendra Pradyumna Pothukuchi, Leon Lufkin, Yu Jun Shen, Alejandro Simon, Rome Thorstenson, Bernardo Eilert Trevisan, Michael Tu, Mudi Yang, Ben Foxman, Viswanatha Srinivas Pothukuchi, Gunnar Epping, Bryant J Jongkees, Thi Ha Kyaw, Jerome R Busemeyer, Jonathan D Cohen, Abhishek Bhattacharjee

-

[arXiv '23] Mitigating Catastrophic Forgetting in Long Short-Term Memory Networks

Ketaki Joshi, Raghavendra Pradyumna Pothukuchi, Andre Wibisono, Abhishek Bhattacharjee

Peer reviewed conferences, journals, and workshops

-

FriendlyFoe: Adversarial Machine Learning as a Practical Architectural Defense against Side Channel Attacks

paper

First use of AML as a dynamic architecture defense.

International conference on Parallel Architectures and Compilation Techniques (PACT), 2024.

Hyoungwook Nam, Raghavendra Pradyumna Pothukuchi, Bo Li, Nam Sung Kim, Josep Torrellas

-

Distributed Brain-Computer Interfacing with a Networked Multi-Accelerator Architecture

paper

IEEE Micro Top Picks special edition, June 2024.

Raghavendra Pradyumna Pothukuchi, Karthik Sriram, Michał Gerasimiuk, Muhammed Ugur, Rajit Manohar, Anurag Khandelwal, Abhishek Bhattacharjee -

SCALO: An Accelerator-Rich Distributed System for Scalable Brain-Computer Interfacing

paper

First BCI capable of interfacing with multiple brain regions. Artifact available.

International Symposium on Computer Architecture (ISCA), 2023.

Best Paper

IEEE Micro Top Picks in Computer Architecture 2024

Karthik Sriram*, Raghavendra Pradyumna Pothukuchi* †, Michał Gerasimiuk, Muhammed Ugur, Oliver Ye, Rajit Manohar, Anurag Khandelwal, Abhishek Bhattacharjee

*Joint first authors †Lead PI

-

HALO: A Hardware-Software Co-Designed Processor for Brain-Computer Interfaces

paper

Partial tape-out of the HALO BCI processor. Picture of packaged chip.

IEEE Micro HotChips special edition, May 2023.

Ioannis Karageorgos, Karthik Sriram, Xiayuan Wen,Ján Veselý, Nick Lindsay, Michael Wu, Lenny Khazan, Raghavendra Pradyumna Pothukuchi, Rajit Manohar, Abhishek Bhattacharjee

-

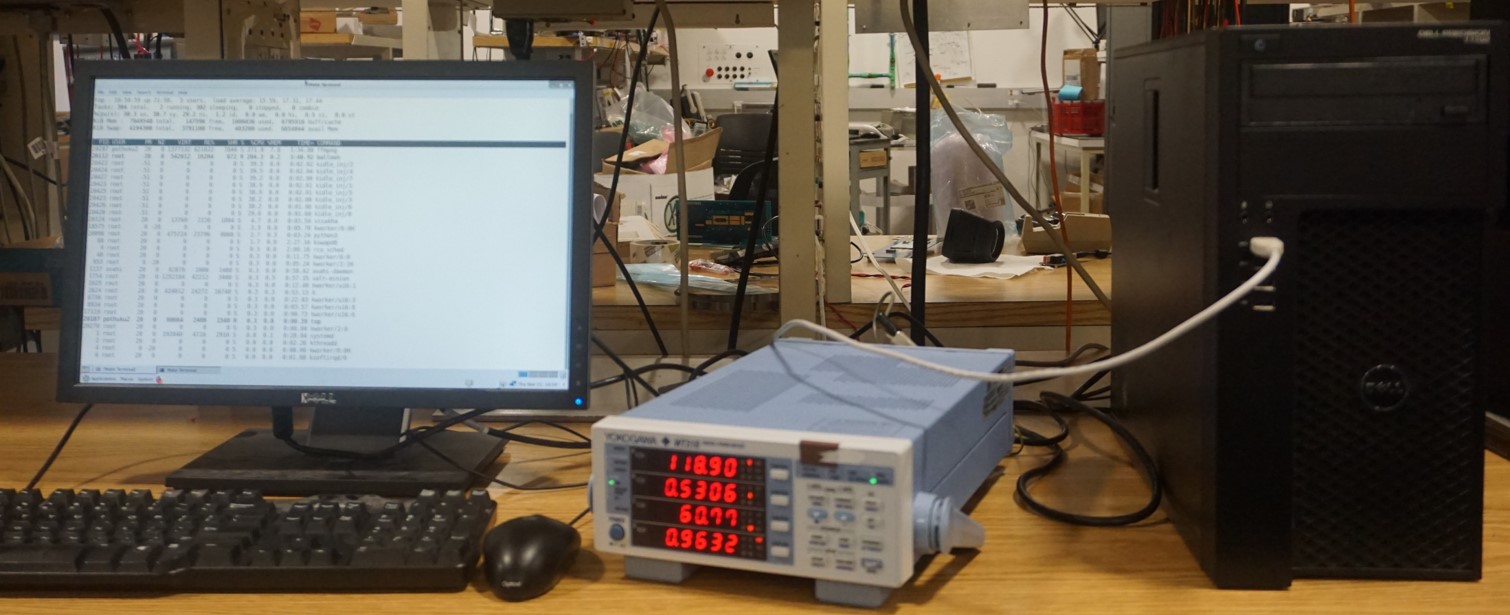

Maya: Using Formal Control to Obfuscate Power Side Channels

paper

IEEE Micro Top Picks special edition, July 2022.

Raghavendra Pradyumna Pothukuchi, Sweta Yamini Pothukuchi, Petros Voulgaris, Alexander Schwing, Josep Torrellas -

Distill: Domain-Specific Compilation for Cognitive Models

paper

Integrated into PsyNeuLink, a cognitive modeling environment. Artifact available.

International Symposium on Code Generation and Optimization (CGO), 2022.

Ján Veselý*, Raghavendra Pradyumna Pothukuchi*, Ketaki Joshi, Samyak Gupta, Jonathan D. Cohen, Abhishek Bhattacharjee

*Joint first authors

-

Maya: Using Formal Control to Obfuscate Power Side Channels

paper

poster

Prototypes: 4-core Intel Haswell, 6-core and 2-socket 20-core Intel Sandybridge servers running Linux. Code released.

International Symposium on Computer Architecture (ISCA), 2023.

IEEE Micro Top Picks in Computer Architecture 2021

Raghavendra Pradyumna Pothukuchi, Sweta Yamini Pothukuchi, Petros Voulgaris, Alexander Schwing, Josep Torrellas

-

Control Systems for Computer Systems: Making computers efficient with modular, coordinated and robust control

paper

IEEE Control Systems, April 2020.

Cover feature [Cover, designed by me]

Raghavendra Pradyumna Pothukuchi, Sweta Yamini Pothukuchi, Petros Voulgaris, Josep Torrellas

-

Tangram: Integrated Control of Heterogeneous Computers

paper

poster

Prototype: Multisocket node with 2 AMD Ryzen CPUs and Radeon Vega GPU running Linux. Tech report released. AMD Patent.

International Symposium on Microarchitecture (MICRO), 2019.

Raghavendra Pradyumna Pothukuchi, Joseph Greathouse, Karthik Rao, Leonardo Piga, Christopher Erb, Petros Voulgaris, Josep Torrellas -

Structured Singular Value Control for Modular Resource Management in Multilayer Computers

paper

First application of robust control for computer architecture.

IEEE Conference on Decision and Control (CDC), 2018.

Raghavendra Pradyumna Pothukuchi, Sweta Yamini Pothukuchi, Petros Voulgaris, Josep Torrellas

-

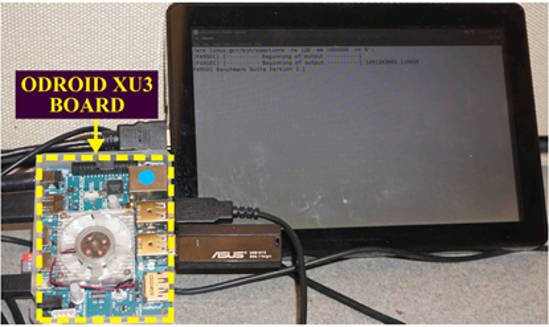

Yukta: Multilayer Resource Controllers to Maximize Efficiency

paper

Prototype: Odroid XU3 board with Samsung Exynos big.LITTLE processor running Linux

International Symposium on Computer Architecture (ISCA), 2018.

2nd prize, IEEE Computer Society Lance Stafford Larson Paper Award

Raghavendra Pradyumna Pothukuchi, Sweta Yamini Pothukuchi, Petros Voulgaris, Josep Torrellas

-

Sthira: Systematically Controlling the

Error Rates in Variation-Prone Networks-on-Chip for

Energy Efficiency

paper

International conference on Parallel Architectures and Compilation Techniques (PACT), 2017.

Best Paper Nominee

Raghavendra Pradyumna Pothukuchi, Amin Ansari, Bhargava Gopireddy, Josep Torrellas -

Using Multiple Input, Multiple Output Formal Control

to Maximize Resource Efficiency in Architectures

paper

First application of optimal MIMO control for computer architecture.

International Symposium on Computer Architecture (ISCA), 2016

3rd prize, IEEE Computer Society Lance Stafford Larson Paper Award

Raghavendra Pradyumna Pothukuchi, Amin Ansari, Petros Voulgaris, Josep Torrellas

Peer reviewed workshops

-

The Interplay of Computing, Ethics, and Policy in Brain-Computer Interface Design

paper

Workshop on Hot Topics in Ethical Computer Systems (HotEthics), 2024.

Muhammed Ugur, Raghavendra Pradyumna Pothukuchi, Abhishek Bhattacharjee

-

Towards Forever Access for Implanted Brain-Computer Interfaces

paper

Workshop on Hot Topics in Ethical Computer Systems (HotEthics), 2024.

Muhammed Ugur, Raghavendra Pradyumna Pothukuchi, Abhishek Bhattacharjee

-

Swapping-Centric Neural Recording Systems

paper

Non-Volatile Memories Workshop (NVMW), 2024.

Muhammed Ugur, Raghavendra Pradyumna Pothukuchi, Abhishek Bhattacharjee

-

Leveraging NVMs for Neural Interface Coverage

paper

Workshop on Emerging Computer Systems Challenges and Applications in Biomedicine (BioSys), 2024.

Muhammed Ugur, Raghavendra Pradyumna Pothukuchi, Abhishek Bhattacharjee

-

Prefetching Using Principles of Hippocampal-Neocortical Interaction

paper

poster

Brain-inspired prefetching.

Workshop on Hot Topics in Operating Systems (HotOS), 2023.

Yale Wu Tsai Institute Research Spotlight

Michael Wu, Ketaki Joshi, Andrew Sheinberg, Guilherme Cox, Anurag Khandelwal, Raghavendra Pradyumna Pothukuchi, Abhishek Bhattacharjee

Poster credit: Michael Wu

Patents

-

A Distributed System of Computer Architectures

Distributed BCI with intelligent on-device processing.

U.S. Provisional Patent Application No. 63/508,760, 2023

Karthik Sriram, Raghavendra Pradyumna Pothukuchi, Rajit Manohar, Anurag Khandelwal, Abhishek Bhattacharjee

-

Distributed Multi-Input Multi-Output Control Theoretic Method to Manage Heterogeneous Systems

Hierarchical resource management for distributed, heterogeneous computers.

U.S. Patent Application No. 15/950,172, April 2018

Raghavendra Pradyumna Pothukuchi, Joseph Greathouse, Leonardo Piga

Technical reports

-

Designing a Robust Controller for Obfuscating a Computer’s Power

paper

Accompanies the MICRO 2019 paper. Includes detailed robust control ( H and mu/SSV) design with code.

UIUC, June 2021

Raghavendra Pradyumna Pothukuchi, Sweta Yamini Pothukuchi, Petros G. Voulgaris, Josep Torrellas

-

A Guide to Design MIMO Controllers for Architectures

paper

Accompanies the ISCA 2016 paper. Includes detailed MIMO control (LQG) design and robustness analysis with code.

UIUC, April 2016

Raghavendra Pradyumna Pothukuchi, Josep Torrellas

Posters and Poster Papers

-

Building the Brain-Memex

poster

MICRO Jobs Forum, 2023.

-

Quantum, Cognition and Computer Systems

poster

poster

Heidelberg Laureate Forum, 2022.

CI Fellows Poster session, NITRD 30th anniversary symposium 2022.

Presenter: Raghavendra Pradyumna Pothukuchi,

PIs (alphabetical order): Abhishek Bhattacharjee, Jerome R Busemeyer, Jonathan D. Cohen, Yongshan Ding, Bryant Jongkees, and Thi Ha Kyaw

Students (alphabetical order): Yasmina. Abukhadra, Nathan Ahn, Yun Da Chua, Gunnar Epping, Ben Foxman, Connor Hann, Lena Rosendahl, Yu Jun Shen, Alejandro Simon, Bernardo Eilert Trevisan, Michael Tu, Jean Wang, Mudi Yang -

Multilayer Compute Resource Management with Robust Control Theory

paper

poster

International conference on Parallel Architectures and Compilation Techniques (PACT), 2017.

Winner, ACM Student Research Competition

Raghavendra Pradyumna Pothukuchi, Sweta Yamini Pothukuchi, Petros Voulgaris, Josep Torrellas

- [AICERA '12] Remote Experimentation of “No-load Tests

on a Transformer” in Electrical Engineering

paper

IEEE International Conference on Engineering Education: Innovative Practices and Future Trends (AICERA), 2012.

Pradyumna P.R., Tarun C.K.S., Bhanot, S.

Grants

Co-PI (under preparation)

-

Next-Generation Computer Architecture for Emergent Symbolic Binding Networks

PI: Abhishek Bhattacharjee, Co-PI: Jonathan D Cohen, John Lafferty, Raghavendra Pradyumna Pothukuchi -

A Flexible Ultra-Low-Power Processors for Implantable Brain-Computer Interfaces

PI: Abhishek Bhattacharjee, Co-PI: Rajit Manohar, Hitten Zaveri, Raghavendra Pradyumna Pothukuchi

Writing support

-

NSF Award #1763658

CSR: Medium: Effective Control to Maximize Resource

Efficiency in Large Clusters; Hardware, Runtime, and

Compiler Perspectives

PIs: Josep Torrellas, Laxmikant Kale, David Padua at UIUC, 2018 -

NSF Award #1725734

SPX: Secure, Highly-Parallel Training of Deep Neural

Networks in the Cloud Using General-Purpose Shared-Memory Platforms

PIs: Josep Torrellas, Christopher Fletcher at UIUC, 2017

Talks

-

Quantum Systems for Cognitive Modeling

Yale Quantum Institute, October 2023 (scheduled) -

Machines that Talk to the Brain and Think Like the Mind

University of Pennsylvania, October 2023 (scheduled)

New York University, October 2023

Rutgers University, October 2023 -

Hull: A New Distributed and Scalable Brain-Computer Interfacing Architecture

Neurostimulation Research Meeting, Yale University, November 2023 -

Intelligent Systems for Extreme-Efficiency and Security

Georgia Institute of Technology, February 2021

University of California at Los Angeles, February 2020

Pennsylvania State University, February 2020

Yale University, November 2019 -

Maya: Using Formal Control to Obfuscate Power Side-channels

Intel Side Channel Academic Program, Workshop, Intel, May 2021

Security and Privacy Research at Illinois (SPRAI), UIUC, September 2019 -

Extreme-Efficiency Computing

Indian Institute of Sciences (IISc), Bengaluru, India, January 2019

Intel Research, Bengaluru, India, January 2019

Indian Institute of Technology (IIT), Delhi, India, January 2019

Rising Stars in Computer Architecture Workshop, Georgia Tech, September 2018